Scientific Research and Essays Vol. 7(8), pp. 865-872, 29 February, 2012 Available online at http://www.academicjournals.org/SRE DOI: 10.5897/SRE12.006

ISSN 1992-2248 ©2012 Academic Journals

# Full Length Research Paper

# New programmable BiCMOS fuzzifier

### Sadeq Aminifar

Department of Electrical Engineering, Mahabad Branch, Islamic Azad University, Mahabad, Iran. E-mail: saminifar@yahoo.com.

Accepted 16 February, 2012

It is clear that fuzzy logic is more compatible with analog circuit implementation compare to its digital mate. On the other hand being programmable is very important in various industrial implementations. Because of that this paper introduces a new method for implementing Membership function in fuzzy logic controllers. And a new high-speed analog fuzzification circuit was introduced for implementing this Idea and verified by Hspice simulations. It is characterized by a trapezoidal membership function with independently adjustable parameters. The core of the circuit is a BiCMOS current-mode circuit which works as a fuzzifier. The speed of controller is 20MFILIPS.

Key words: Fuzzifier, fuzzy controller, current-mode circuits, Mixed-Mode and BiCMOS.

### INTRODUCTION

There are various circuit implementation methods CMOS, Bipolar and BiCMOS. In this paper we preferred BiCMOS implementation. BiCMOS is an evolved semiconductor technology that integrates two formerly separate semiconductor technologies - those of the bipolar junction transistor and the CMOS transistor - in a single integrated circuit device.

Bipolar junction transistors offer high speed, (Fuller et al., 2000; Min-Yuan Cheng et al., 2010; Rong-Jong Wai et al., 2002) high, and low output resistance, which are excellent properties for high-frequency analog amplifiers, whereas CMOS technology offers high input resistance and is excellent for constructing simple, low-power logic gates.

For as long as the two types of transistors have existed in production, designers of circuits utilizing discrete components have realized the advantages of integrating the two technologies (Meghraj Kachare et al., 2005); however, lacking implementation in integrated circuits, the application of this free-form design was restricted to fairly simple circuits. Discrete circuits of hundreds or thousands of transistors quickly expand to occupy hundreds or thousands of square centimeters of circuit board area, and for very high-speed circuits such as those used in modern digital computers, the distance between transistors (Mamdani et al., 1997; Hiroyuki

Watanabe et al., 1990) also makes the desired speeds grossly unattainable, so that if these designs cannot be built as integrated circuits, then they simply cannot be built.

Analog approaches are inherently faster and require much smaller silicon area and lower power consumption (Baturone et al., 1997, 1998; Nakamura et al., 2004). Their main disadvantage is that they are not so easily programmable. In this paper we present a new high-speed current-mod fuzzifier characterized by a trapezoidal membership function.

The fuzzifier presented in this paper suitable circuit to analyze and tune the nonlinear parameters of membership functions. These techniques provide a method for the fuzzy modeling procedure to learn information about a data set, in order to compute the membership function parameters that best allow the associated fuzzy inference system to track the given input/output data. This learning method works similarly to that of neural networks. Our discussions are started with summery of Nero-Fuzzy structures and back propagation algorithm and then describing BiCMOS structure along with circuit designs of fuzzifier.

In fact, because of that it is difficult to analyze highly nonlinear systems with classic methods, we convert classic world data into corresponding language terms.

Figure 1. Considering fuzzy as a new mapping space.

Figure 2. The shape of a trapezoidal membership functions with different slopes.

This application is said "fuzzifying" (Figure 1).

Therefore, for mapping classic world to fuzzy world, we need a circuit said Membership Function MFC. It is introduced a new design strategy for Fuzzifier implementation, in this paper. This method is the result of a new design method for digital fuzzy logic controller.

In this method all inputs and outputs of whole system are digital data, but the structure of different internal blocks is nearly analog.

### **Fuzzy membership definition**

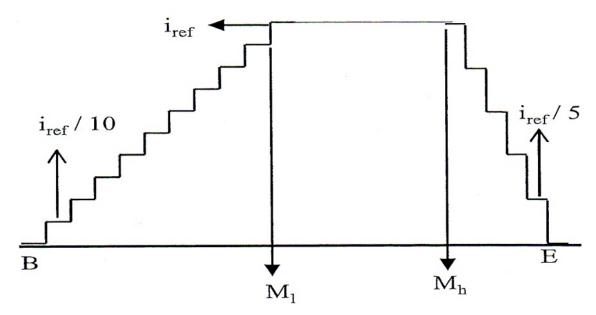

It is clear that general shape of a membership function which include triangle and ascending and descending ramps is as the nonsymmetrical trapezoidal shown in Figure 2, in which B is start point and E is the end, from B

to MI and from Mh to E are ascending and descending slops, respectively (Sadeq A, et al., 2011). The interval between MI and Mh is plateau region which its value is corresponding to logical one.

In the strategy we introduced, input signal is digital and output membership degree is analog. As a result, we have considered horizontal axes as a digital data 5-bit (32 different binary states), but vertical axes as an analog signal in current-mode. It works in the range 58 A range.

The membership degree is as different and specific levels of current. Each level is a coefficient of a base current and this base current is specified according to the ascending and descending slopes.

The worst-case error is 1.3  $\mu$ A, which is equal to 5-bit resolution. The circuit presented for fuzzifier is capable of performing different membership function shapes with deferent slopes.

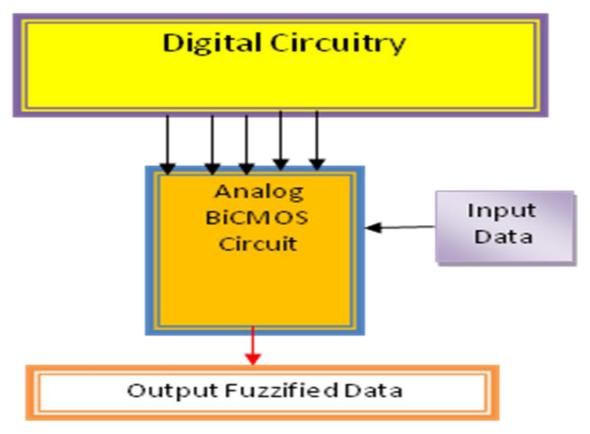

Figure 3. The relation between digital and analog part of Fuzzifier.

For example: if we chose  $d_1 = d_1$ ,  $M_1 < M_2$ , it results a symmetric trapezoidal membership function.

Now, if we want to have descending slops with lesser slop, we have to choose larger amplitude for dl. There is an example in the Figure 2. If E =  $M_1$  =  $M_h$ , E = B + 6 then  $i_{base}$  =  $I_{ref}$ /5 and the amplitude of levels are  $i_{ref}$ 5,  $2i_{ref}$ 5,  $3i_{ref}$ 5,  $4i_{ref}$ 5,  $5i_{ref}$ 5 =  $I_{ref}$ .

Changing E, we will have different descending slopes as described for some different values of B.

For ascending slopes, changing B with constant  $M_1=M_h=E$ , we can similarly perform any arbitrary slop, for example if If  $E=M_1=M_h$ , E=B+11 then  $I_{base}=I_{ref}/10$  and the amplitude of levels are  $i_{ref}/10$ ,  $2i_{ref}/10$ ,  $3i_{ref}/10$ ,  $4i_{ref}/10$ ,  $5i_{ref}/10$ ,  $6i_{ref}/10$ ,  $7i_{ref}/10$ ,  $8i_{ref}/10$ ,  $9i_{ref}/10$ ,  $10i_{ref}/10=i_{ref}$ , as shown in Figure 2.

Considering examples mentioned above for performing ascending and descending slopes, choosing different values for parameters, we can have different triangular and trapezoidal shapes for performing membership functions, symmetrically or asymmetrically. There are some examples for clarification. Given  $M_1$ ,  $M_1$ ,  $M_2$ ,  $M_3$ ,  $M_4$ ,  $M_5$ ,

current becomes  $2i_{ref}$  /1 0, when I = B + 1° then output current will become reference current ( $I_{ref}$ ). The descending slop of triangular has five steps while the step with  $I_{ref}$  amplitude is common between ascending and descending slopes. The base current in that case is one fifth of reference current. The output current in M1 = M, is equal to reference current which is decreased  $I_{ref}$  /5 for everyone step respect to increasing input digital signal (I). That is, if I = MI + 1 then output current is equal to  $I_{ref}$  -  $I_{ref}$  /5 and output current will be lout = 3  $I_{ref}$  /5 as if I = Mi + 2. IfI = E then output current discusses to zero.

It was illustrated an unsymmetrical trapezoidal membership function in the Figure 2. The both side slops of this membership function are the same as the triangular membership function mentioned above. But in this case we have different  $M_1$  and  $M_h$ . The output current will remain reference current from  $M_1$  to  $M_h$ .

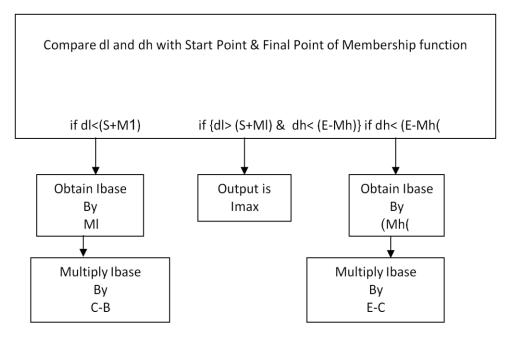

### The fuzzifier circuit algorithm

The main idea of the fuzzifier circuit is shown in Figure 3. Crisp input signal and the chosen parameters for performing favorable membership function, are applied to switch controller block and the output of this block are digital signals which control BiCMOS analog part.

Figure 4. Block diagram of idea which fuzzifier has designed on it.

Input parameters are 5-bit numbers (B,  $M_1$ ,  $M_h$ , E, d., dh) introduced in Figure 2. According to these parameters, the quotient is  $I_{base}$ .  $I_{Base}$  will be multiplied by ordinal numbers between Band E.

If input signal is smaller than B or greater than E, the switches of right part of circuit will be disconnected and output current will be zero.

The more detailed way fuzzifier circuit works is illustrated in Figure 4. Considering the selection of parameters mentioned in Figure 2, all normalized membership functions only could take this values mentioned bellow for membership degree.

### **Fuzzifier circuit**

Considering the descriptions mentioned before, and according to the B, MI, Mh and E parameters, at first we have a division, which its numerator is reference current and its denominator is  $d_1 = M_1 - B$  or  $d_2 = E - M_h$ .

Figure 3 illustrates the different blocks of fuzzifier structure, and all blocks are illustrated in the Figure 5 in details. The dl and dh parameters at first entered to the carry generator part and considering previous description this action will be done with two separate parts, one for stimulate Linear voltage to current converter (LVCC) circuit. At last the obtained output of right current mirrors enters Gilbert translinear cells (GTC) which is discussed in detail (Jimenez et al., 1995).

The output current, lout, is zero for negative input voltages Vd<0 (where Vd=VI- V2). It has a linear region

with constant slope s=I/R for 0<Vd<di and it saturates with a current I, for Vd>IR. For Vd<0 the differential-pair current flows through transistor Match. This transistor works similar to a catch diode: it provides a path for negative currents to flow and prevents large voltage swings at the output node of the differential pair. This avoids degradation of the speed of the circuit this has a linear region in the range Va<Vin<Vb. The left LVCC is used to set the bias (saturation) current of the right LVCC to a value lba=(Vb-Va)/R. The output current of the right LVCC has the transconductance characteristic with a linear region in the range Va<Vin<Vb, slope s=I/R and saturation current lba=(Vb-Va)/R. A similar Arrangement is used to produce a Tran conductance Characteristic with a linear region Vic<Van<DVD and with saturation current (for Van>DVD) led= (Vd-Vc)/R. The all current sources shown in Figure 5 are equal and their size is 33

All currents are equal and in linear regions in the ranges Va<Vin<Vb and Vc<Vin<Vd respectively. The GTC is current multiplier/divider.

In Figure 5 for the left GTC li= (Vin-Vb)/R, li=(Vb-Va)/R and lout=lamp. The output current is given by l<=lol=lamp (Vin-Va)/(Vb-Vc). It has the piecewise linear characteristic shown on the left of Figure 5. Variables and parameters cart be defined in the current domain according tor, lamp=Vamp/R, lin=Vm/R, Ja=Va/R, lb=Vb/R, lc=Vc/R and ld=Vd/R. In this case the circuit of Figure 5 alone can be considered a current-mode fuzzifier. Currents lin/ lamp, la, and lc can be replicated (and rectified) using current mirrors.

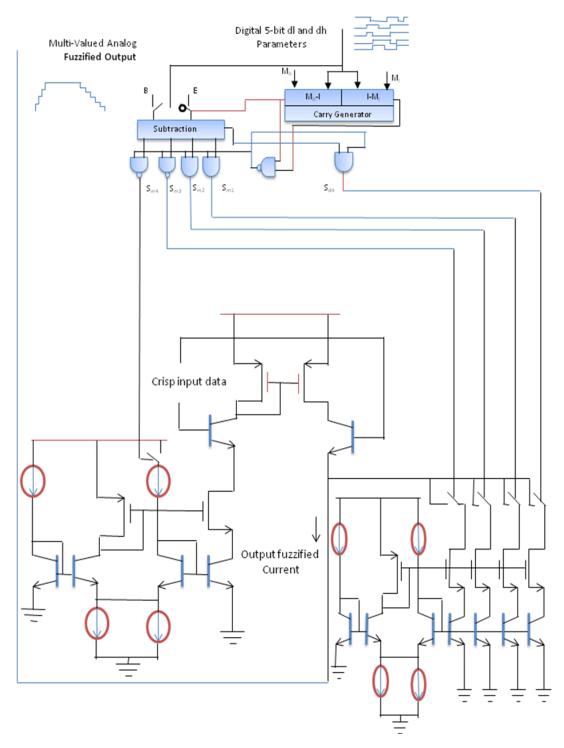

Figure 5. Proposed BiCMOS Fuzzifier.

## Digital circuitry for switches controlling

The digital circuit illustrated below is used to control switches, shown in analog circuit in Figure 5. This structure was established of as-bit subtraction and two 5-

bit carry generator circuits and some extra logic gates and switches.

The dI and d, four-bit parameters are applied to this structure and will generate  $S_{\text{dI}}$  to  $S_{\text{d3}}$  for applying to LVCC circuit.

Figure 6. The obtained various MFCs.

Applying E, B and input signal (1) to this circuit yields  $S_{ml}$ ,  $S_{m2}$ ,  $S_{m3}$ , and  $S_{m4}$  for controlling GTC circuit.

$S_{d4}$  and  $S_{d5}$  are produced to choose either Block I or Block 2, in order to specify the reference current is divided over one to fifteen.

#### **RESULTS**

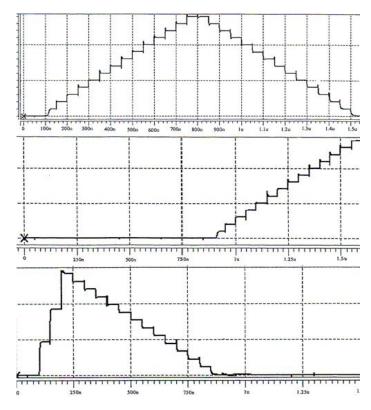

HSPICE simulations using 2  $\mu m$  BiCMOS technology N-well parameters (MOSIS) were performed. P and N transistors with dimensions 24/2 and 12/2 (in  $\mu m$ ) were used for the simulations. Figure 6 shows the HSPICE simulated transfer characteristic of the fuzzifier circuit of Figure 5. The high speed rectifying characteristic can be verifed with the transient response to a IV, 10 MHz sine wave signal.

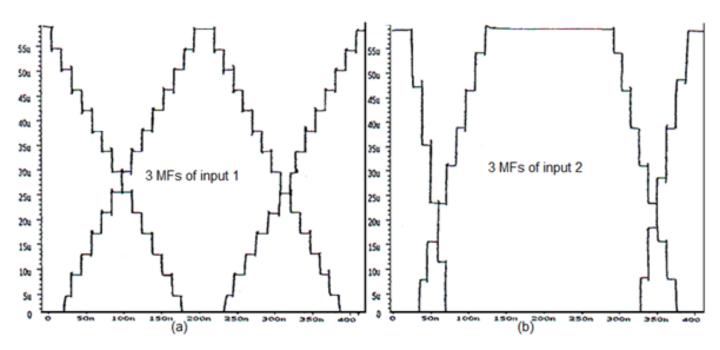

Figure 7 shows the trapezoidal DC transfer characteristic of the overall circuit for Va=OV, Vb=0.75 V, Vc=1.75 V and Vd=3 V. The systematic model of controller was evaluated using Anfis architecture training. To start training an FIS, first we need to have a training data set that contains desired input/output data pairs of the target system to be modeled. Sometimes we should have the optional testing data set that can check the generalization capability of the resulted FIS. Therefore the checking data set helps with model over fitting during

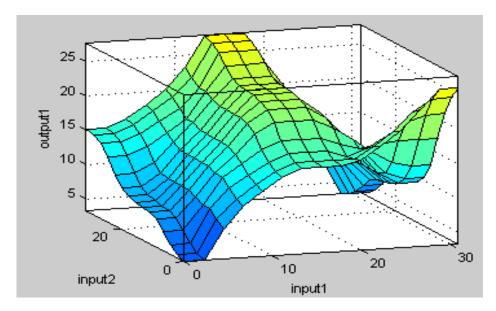

the training. The next stage is to specify initializing and generating of FIS parameters for Anfis training. In this paper we initialize the FIS with two inputs which one of them has three membership functions as shown in Figure 7a and the other one has three Trapezoidal shapes as shown in Figure 7b, nine rules and one output. After training, the improved and changed membership functions are obtained and shown in Figure 7. The total extracted control surface of controller is introduced and illustrated in Figure 8.

### DISCUSSION

E. Alarcon (Alarcon et al., 1999) implemented a fuzzifier with a different stategy. They used the concept of the implicit signal-lo-time conversion in the PWM process. M. Azeem (Mohammad Fazel Azimi et al., 2006) proposed a fuzzifier for Sugeno-Takagai's fuzzy logic controller. They used normal current-mode dividers.

The analog implementation of a generalized fuzzification scheme was introduced in (Sanchez et al., 2002).

The work which has done in this paper compare to works mentioned above has better functionality and compatibility. High speed operation was also verified with simulations. The scheme uses circuits which can operate

Figure 7. Hspice simulations output of proposed fuzzifier which produces all types of membership functions applicable to a two-input one-output controller.

Figure 8. The obtained control surface of proposed controller.

with low supply voltages (single 3.3 V supply) and requires very compact circuitry (less than 30 transistors). It can find utilization in applications where high adaptable fuzziliers with constant singleton coefficients are required. The main drawback of this work is the problem of fabrication due to using both NPN and PNP bipolar transistor types with CMOS transistors.

### Conclusion

This paper introduces a new method for implementing Membership functions in fuzzy systems. And a new high-speed analog fuzzification circuit was introduced for implementing this Idea and verified by simulations. It is characterized by a trapezoidal membership function with

independently adjustable parameters. The core of the circuit is a BiCMOS current-mode circuit which works as a fuzzifier. This scheme is expected to find application in neuro-fuzzy processors where adaptation of the membership function parameters is required. The result is a faster, cheaper and higher controllable compare to conventional fuzzification techniques This fuzzifier has applied to a two input one output controller and has shown good results.

#### **ACKNOWLEDGEMENT**

The author would like to thank Mahabad branch, Islamic Azad University for supporting this research.

#### **REFERENCES**

- Alarcon E, Poveda A, Madrenas I, Vidal E, Gom5riz S, Guinjoad F (1999). Novel Pulse-Width-Modulated Current-Mode Analog Defuzzifier for the Fuzzy Control of Switching DC-DC Converters, 0-7803-5491, IEEE

- Sanchez F, Cobo JEA (2002). Design of High Complexity Fuzzy Controllers using Generic VHDL for Appliance Applications. VIII Int. Workshop chip IWS2002. Guadalaiara, Mexico.

- Jimenez C, Sanchez-Solano S, Barriga A (1995). Hardware implementation of a general purpose fuzzy controller. in Proc. 6th IFSA World Congress, pp. 185-188.

- Baturone I, Huertas L, Barriga A, Sinchez-Solano S (1998). Voltage-mode multiple input maximum circuit. Electron. Lett., 30(9): 678-680.

- Baturone L, Sdnchez-Solano S, Barriga A, Huertas L (1997). Implementation of CMOS fuzzy controllers as mixed-signal IC's. IEEE Trans. Fuzzy Syst., 5(1): 1-19.

- Fuller R (2000). Introduction to Nero-Fuzzy Systems. Advances in Soft Computing Series, Springer-Verlag, Berlin.

- Hiroyuki W, Wayne D, Kathy EY (1990). A VLSI Fuzzy Logic Controller with Reconfigurable. IEEE J. SolidState Circuits, 25.

- Nakamura L, Lin C, shen P (2004). A fuzzy neural network speed controller for permanent-magnet synchronous motor drive. IEEE trans. fuzzy syst., 9(5): 751-759.

- Meghraj K, Jaime R, Ramón G, Antonio J (2005). New low-voltage fully programmable CMOS triangular/trapezoidal function generator circuit. IEEE Trans. Circuits Syst., 52(10): 2033-2042.

- Mohammad FA, Member IEEE, Kanu PG (2006). Design Of Analog CMOS Based Fuzzy Inference System. IEEE International Conference on Fuzzy Systems Sheraton Vancouver Wall Centre Hotel, Vancouver, BC, Canada, July 16-21, 2006

- Min-Yuan C, Hsing-Chih T, Erick S (2010). Evolutionary fuzzy hybrid neural network for project cash flow control. Eng. Appl. Artif. Intell., 23(4): 604-613.

- Rong-Jong W (2002). Hybrid fuzzy neural-network control for nonlinear motor-toggle servo mechanism. IEEE Trans. Control Syst. Technol. IEEE Trans., 10: 519-532.

- Sadeq A, Muhammadamin D, Ghader Y (2011). Designing of A Novel FLC as a Digital Chip, J. Basic Appl. Sci. Res., 1(10): 1423-1432.